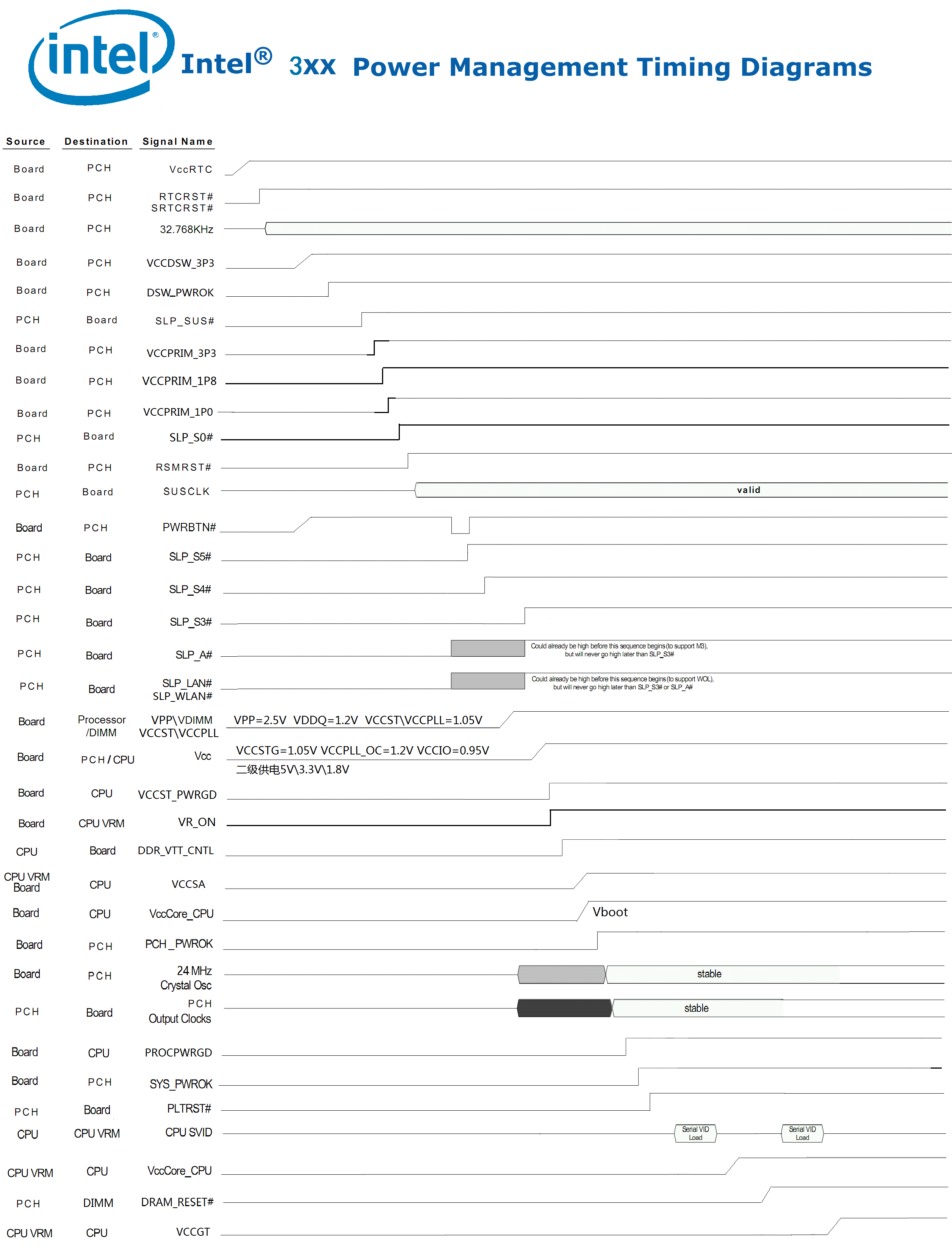

Intel 3xx Power Management Timing Diagrams

时序图:

信号名介绍:

VCCRTC:从CMOS电池或内置电池送给桥的3V供电,给桥的RTC电路供电,以保存CMOS参数和时间运行,此电压不能低于2V RTCRST#/SRTCRST#:主板给桥的两个3V高电平,第一个是RTC电路的复位信号,第二个是ME 模块的复位信号,俩个复位信号的时间不能低于18ms 32.768KHz:桥旁边的32.768KHz晶振,桥给晶振供电,晶振提供频率给桥 VCCDSW_3P3:桥的深度睡眠待机电压,3.3V,不支持深度睡眠时,此电压和VCCPRIM_3P3连在一起 DSW_PWROK:桥的深度睡眠待机电压好,3.3V,不支持深度睡眠时,此信号与RSMRST#连在一起 SLP_SUS#:桥发出的深度睡眠状态指示信号。可用于控制主待机电压的开启和关闭,不支持深度睡眠时,此信号悬空 VCCPRIM_3P3:桥的主待机电压,3.3V VCCPRIM_1P8:桥的主待机电压,1.8V VCCPRIM_1P0:桥的主待机供电,1.0V SLP_S0#:当PCH和CPU处于空闲状态时。此信号将去控制CPU供电进入轻负载模式,也可以连接到EC,用于其他电源管理 RSMRST#:桥的主待机电压好,3.3V,也是PCH内部ACPI控制器的复位,ACPI控制器从VCCPRIM_3P3正常后开始复位,复位时间不能低于10ms SUSCLK:桥发出的32.768KHz时钟,从RSMRST#完成复位后97ms开始动作,但此信号不一定被主板采用 PWRBTN#:桥收到的下降沿触发信号,3.3V-0V-3.3V,通知桥退出睡眠状态 SLP_S5#:桥收到PWRBTN#后,置高SLP_S5#成3.3V,表示退出关机状态 SLP_S4#:桥置高SLP_S4#成3.3V,表示退出休眠状态,用于开启内存供电 SLP_S3#:桥置高SLP_S3#成3.3V,表示退出睡眠状态,进入S0开机状态,用于开启桥供电,总线供电 SLP_A#:此信号一般不采用,因为桥取消了ME模块供电和APWROK,APWROK被集成在桥里 SLP_LAN#:网卡的供电控制信号,除Think PAD外,其他机型基本不采用此信号 VDDIMM,VPP,VCCST,VCCPLL:指内存供电1.2V,VPP供电2.5V,VCCST和VCCPLL供电1.0V,一般受控于SLP_S4# VCC:之二级电压3.3V/5V,1.8V,总线供电(VCCIO)0.95V,VCCPLL_OC供电1.2V,VCCSTG供电1.05V等 VCCST_PWRGD:指VCCST供电和其他供电正常后,送给CPU的电源好信号,1.0V VR_ON:主板给CPU电源管理芯片的开启信号,用于开启VCCSA供电和CPU核心供电VBOOT电压 DDR_VTT_CNTL:CPU发出的内存VTT供电开启信号,用于控制产生0.6V内存VTT供电 VCCSA:给CPU的系统代理供电1.05V VccCORE_CPU:CPU核心供电的VBOOT电压1V左右,通常在总线供电正常后产生 PCH_PWROK:主板给桥的3.3V高电平,表示S0状态电压都OK 24MHzCrystal Osc:桥得到供电后,桥的24M晶振开始起振,给桥内部的时钟模块提供基准频率 PCH Output Clocks:桥得到PCH_PWROK后读取ME配置脚位后,输出各组时钟 PROCPWROK:桥发给CPU的PG,表示CPU 的核心电压OK,1.05V SYS_PWROK:表示系统供电正常,是产生复位的关键信号,3.3V PLTRST#:桥发出的平台复位3.3V,给各芯片,插槽作为复位 CPU SVID:当CPU收到PROCPWRGD后,CPU发出SVID给CPU供电芯片,用于重新调整CPU核心供电 VCCCORRE_CPU:CPU供电芯片控制输出SVID调整后的CPU核心供电 DRAM_RESET#:CPU满足了各个供电,时钟,复位信号后,开始读取BIOS自检,在自检的过程中,当桥通过SMBUS完成内存识别后,桥发出DRAM_RESET#给内存插槽,用与内存复位 VCCGT:自检过内存后,CPU再次发出SVID给电源管理芯片,控制产生集显供电,0.7v-1.3v

|